Spectre90

Newbie level 6

- Joined

- Nov 15, 2014

- Messages

- 11

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1

- Activity points

- 85

Language: Verilog

Board: Xilinx Basys2

Hi

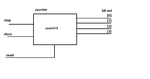

I am trying to make a counter that has a reset, clock (board's speed 50MHz), and a manual stop button inputs and outputs are 4-bits for a 7-segment-display.

However, i am trying to count from 1 to 9 (of course in a loop) and if i pressed the stop button, my output will be whatever the clock counted.

Also if reset is high, count goes back to 1.

i tried it but it doesnt work and i need help now.

Here is my code:

Board: Xilinx Basys2

Hi

I am trying to make a counter that has a reset, clock (board's speed 50MHz), and a manual stop button inputs and outputs are 4-bits for a 7-segment-display.

However, i am trying to count from 1 to 9 (of course in a loop) and if i pressed the stop button, my output will be whatever the clock counted.

Also if reset is high, count goes back to 1.

i tried it but it doesnt work and i need help now.

Here is my code:

Code Verilog - [expand]

Attachments

Last edited by a moderator: