subramaniam1990

Newbie level 3

- Joined

- Mar 19, 2013

- Messages

- 3

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,281

- Activity points

- 1,310

hi,

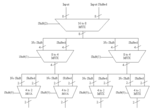

I am currently working on a project on implementation of floating point arithmetic...in that i have to implement barrel shifter. .. iam using verilog coding for it..i have coded it...can you just tell me if its right..it will be great if you could help me out..i would like to know if I am moving in right direction.. thank you

this code is for shifting it towards right:

module barrel_shifter(ip , op , shift , clk, load_in , load_out , load_shift);

input ip[31:0];

input shift[4:0];

input clk;

input load_in;

input load_out;

input load_shift;

output op[31:0];

always @(load_in,clk)

begin

if(clk==1)

begin

if(load_in == 1)

begin

buffer_in <= ip;

end

else

begin

buffer_in <= 0;

end

end

end

always @(load_shift,clk)

begin

if(clk==1)

begin

if(load_shift == 1)

begin

buffer_shift <= shift;

end

else

begin

buffer_shift <= 00000;

end

end

end

always @(load_in , load_shift , buffer_in, buffer_shift)

begin

if(buffer_shift[4] == 1)

begin

out_shift4 <= {buffer_in[15:0],buffer_in[31:16]};

end

else

begin

out_shift4 <= buffer_in;

end

end

always @(load_in , load_shift , buffer_shift, out_shift4)

begin

if(buffer_shift[3] ==1'b1)

begin

out_shift3 <= {out_shift4[7:0],out_shift4[31:8]};

end

else

begin

out_shift3 <= out_shift4;

end

end

always @(load_in , load_shift , buffer_shift, out_shift3)

begin

if(buffer_shift[2] ==1)

begin

out_shift2 <= {out_shift3[3:0],out_shift3[31:4]};

end

else

begin

out_shift2 <= out_shift3; //check condition

end

end

always @(load_in , load_shift , buffer_shift, out_shift2)

begin

if(buffer_shift[1] ==1)

begin

out_shift1 = {out_shift2[1:0],out_shift2[31:2]};

end

else

begin

out_shift1 <= out_shift2; //check condition

end

end

always @(load_in , load_shift , buffer_shift, out_shift1)

begin

if(buffer_shift[0] ==1)

begin

out_shift0 <= {out_shift1[0],out_shift1[31:1]};

end

else

begin

out_shift0 <= out_shift1; //check condition

end

end

always @(clk, load_out)

begin

if(clk==1)

begin

if(load_out==1)

begin

op = out_shift1;

end

else

begin

op = 0;

end

end

end

endmodule

is this code fine or should i use case statements directly using diff combinations as case statements..

regards

subramaniam

I am currently working on a project on implementation of floating point arithmetic...in that i have to implement barrel shifter. .. iam using verilog coding for it..i have coded it...can you just tell me if its right..it will be great if you could help me out..i would like to know if I am moving in right direction.. thank you

this code is for shifting it towards right:

module barrel_shifter(ip , op , shift , clk, load_in , load_out , load_shift);

input ip[31:0];

input shift[4:0];

input clk;

input load_in;

input load_out;

input load_shift;

output op[31:0];

always @(load_in,clk)

begin

if(clk==1)

begin

if(load_in == 1)

begin

buffer_in <= ip;

end

else

begin

buffer_in <= 0;

end

end

end

always @(load_shift,clk)

begin

if(clk==1)

begin

if(load_shift == 1)

begin

buffer_shift <= shift;

end

else

begin

buffer_shift <= 00000;

end

end

end

always @(load_in , load_shift , buffer_in, buffer_shift)

begin

if(buffer_shift[4] == 1)

begin

out_shift4 <= {buffer_in[15:0],buffer_in[31:16]};

end

else

begin

out_shift4 <= buffer_in;

end

end

always @(load_in , load_shift , buffer_shift, out_shift4)

begin

if(buffer_shift[3] ==1'b1)

begin

out_shift3 <= {out_shift4[7:0],out_shift4[31:8]};

end

else

begin

out_shift3 <= out_shift4;

end

end

always @(load_in , load_shift , buffer_shift, out_shift3)

begin

if(buffer_shift[2] ==1)

begin

out_shift2 <= {out_shift3[3:0],out_shift3[31:4]};

end

else

begin

out_shift2 <= out_shift3; //check condition

end

end

always @(load_in , load_shift , buffer_shift, out_shift2)

begin

if(buffer_shift[1] ==1)

begin

out_shift1 = {out_shift2[1:0],out_shift2[31:2]};

end

else

begin

out_shift1 <= out_shift2; //check condition

end

end

always @(load_in , load_shift , buffer_shift, out_shift1)

begin

if(buffer_shift[0] ==1)

begin

out_shift0 <= {out_shift1[0],out_shift1[31:1]};

end

else

begin

out_shift0 <= out_shift1; //check condition

end

end

always @(clk, load_out)

begin

if(clk==1)

begin

if(load_out==1)

begin

op = out_shift1;

end

else

begin

op = 0;

end

end

end

endmodule

is this code fine or should i use case statements directly using diff combinations as case statements..

regards

subramaniam