RFchild

Newbie level 4

Hi, I’m a student.

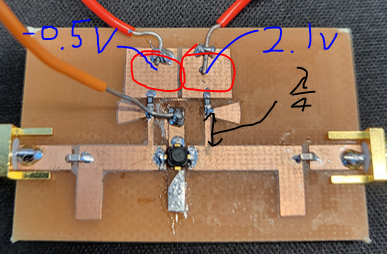

I designed LNA using renesas’s jfet NE3511S02.

But I have some problem.

I designed the rf choke using 4 lambda, but does the length of the red hit part in the picture matter?

And I mesured the circuit using network analyzer, then the transistor is dead.

And I mesured the circuit using network analyzer, then the transistor is dead.

Did I accidentally design the rf choke and get a oscillation and die?

Or did TR die when soldering?

On ADS simulation, stability mu is more than 1. But stability factor k is less than 1.

Is it the matter?

I designed LNA using renesas’s jfet NE3511S02.

But I have some problem.

I designed the rf choke using 4 lambda, but does the length of the red hit part in the picture matter?

Did I accidentally design the rf choke and get a oscillation and die?

Or did TR die when soldering?

On ADS simulation, stability mu is more than 1. But stability factor k is less than 1.

Is it the matter?