Alex Liao

Member level 4

Hi guys,

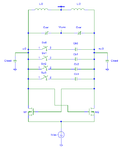

In my VCO design, if I introduce a fixed capacitance, Cap_fix into the C tank, it works fine and give me the target frequency I want. If I disconnect this path (in parallel with the total C) to disable the introduction of this Cap_fix, it gives me higher frequency and it is reasonable as it follows:

w = 1/sqrt(C*L).

But if I want to implement this on/off feature using a MOSFET it does not work.

It always generates strange frequency. I was observing the target frequency through Cadence DFT function of the output in the ADE panel.

Working as a switch, I treated the D and S ends as the switch's two ends. I biased the MOSEFT in triode (ohmic) region, which means,

give me a small Ron (1/gds) when it is on and a infinite large Ron when it is off. For MOSFET size, I tried several combinations, still not working. Either the harmonic signal's strength is high or sometimes output some unreasonable DFT waveform.

Is it such tricky on just using a triode region MOSFET as a simple on/off switch in RF circuit? Or was I implementing the switch using MOSFET in a wrong way? or any tips on bias or sizing this MOSFET? Shouldn't be the reason of my core design as it works fine by simply connecting/disconnect a regular capacitor into the LC tank.:???:

Any reply is appreciated!

Thanks,

Alex

In my VCO design, if I introduce a fixed capacitance, Cap_fix into the C tank, it works fine and give me the target frequency I want. If I disconnect this path (in parallel with the total C) to disable the introduction of this Cap_fix, it gives me higher frequency and it is reasonable as it follows:

w = 1/sqrt(C*L).

But if I want to implement this on/off feature using a MOSFET it does not work.

It always generates strange frequency. I was observing the target frequency through Cadence DFT function of the output in the ADE panel.

Working as a switch, I treated the D and S ends as the switch's two ends. I biased the MOSEFT in triode (ohmic) region, which means,

give me a small Ron (1/gds) when it is on and a infinite large Ron when it is off. For MOSFET size, I tried several combinations, still not working. Either the harmonic signal's strength is high or sometimes output some unreasonable DFT waveform.

Is it such tricky on just using a triode region MOSFET as a simple on/off switch in RF circuit? Or was I implementing the switch using MOSFET in a wrong way? or any tips on bias or sizing this MOSFET? Shouldn't be the reason of my core design as it works fine by simply connecting/disconnect a regular capacitor into the LC tank.:???:

Any reply is appreciated!

Thanks,

Alex