kooheyakhi

Newbie level 4

- Joined

- Jul 8, 2014

- Messages

- 5

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1

- Activity points

- 67

Hello there,

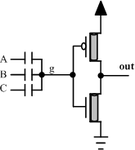

I have designed a 3-input NAND gate by capacitor network connected to a NOT gate.

this circuit functions well. recently i have found out that when inputs are stable and a noise occurs in node g, functionality of my circuit fails. this is because of node g which is floating point of my circuit. given that inputs are logical "111" and supply voltage is 0.65v. in this case, voltage level of node g is 0.65v (can be proved by super position).

now if a spike or noise ocurs and leads to pull node g to ground, then this node never comes back to Vdd and will stay at 0v.

is there any one help me?? the structure of circuit is in the following

I have designed a 3-input NAND gate by capacitor network connected to a NOT gate.

this circuit functions well. recently i have found out that when inputs are stable and a noise occurs in node g, functionality of my circuit fails. this is because of node g which is floating point of my circuit. given that inputs are logical "111" and supply voltage is 0.65v. in this case, voltage level of node g is 0.65v (can be proved by super position).

now if a spike or noise ocurs and leads to pull node g to ground, then this node never comes back to Vdd and will stay at 0v.

is there any one help me?? the structure of circuit is in the following