klpang1

Junior Member level 2

Hi all,

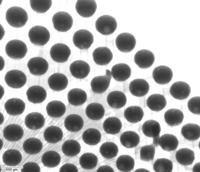

Most of our boards uses FPGA, ASICS and Processors in BGA package which may have about 900 pins each.

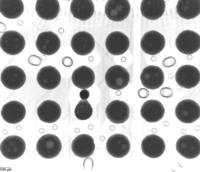

What is the usual method that is used to detect for dry joint on these BGA?

I am searching high and low for such a capability but to no avail. Our PCBA supplier wants nothing to do with reworking BGA as they claim that do not have such a capability. Does anyone has any ideas on the usual method to do so?

Even desoldering and reflow the component that we suspect may pose a risk as the supplier refuse to accept responsibility should the board be damage in process (pad comes off). Is BGA such a difficult thing to work with? Or are they any steps that we should adhere to in the removing and resoldering BGA's?

Any ideas? Appreciate it.

Thanks.

Best rgds,

KaKiaYam

Most of our boards uses FPGA, ASICS and Processors in BGA package which may have about 900 pins each.

What is the usual method that is used to detect for dry joint on these BGA?

I am searching high and low for such a capability but to no avail. Our PCBA supplier wants nothing to do with reworking BGA as they claim that do not have such a capability. Does anyone has any ideas on the usual method to do so?

Even desoldering and reflow the component that we suspect may pose a risk as the supplier refuse to accept responsibility should the board be damage in process (pad comes off). Is BGA such a difficult thing to work with? Or are they any steps that we should adhere to in the removing and resoldering BGA's?

Any ideas? Appreciate it.

Thanks.

Best rgds,

KaKiaYam