wjxcom

Full Member level 5

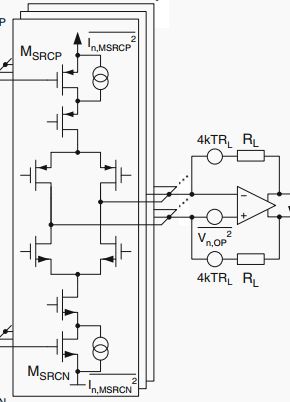

Hi all, design a 12bits, 50MHz DAC. The schematic diagram is as follows. What puzzles me is how to determine the swing rate and bandwidth of the amplifier? I use a two-stage amplifier.

I assume that the output signal of the amplifier is V=A * sin (2 * 3.14 * f * t), so dV/dt = 2 * 3.14 * f *A * cos (2 * 3.14 * f * t). If A = 1.2V and f = 50MHz, the slew rate will be about 2 * 3.14 * 50MHz * 1.2 ≈ 376V/ us. This value is too big! Maybe I made a mistake? Help me please, thanx!!

I assume that the output signal of the amplifier is V=A * sin (2 * 3.14 * f * t), so dV/dt = 2 * 3.14 * f *A * cos (2 * 3.14 * f * t). If A = 1.2V and f = 50MHz, the slew rate will be about 2 * 3.14 * 50MHz * 1.2 ≈ 376V/ us. This value is too big! Maybe I made a mistake? Help me please, thanx!!