mpig09

Full Member level 4

- Joined

- Aug 26, 2005

- Messages

- 232

- Helped

- 8

- Reputation

- 16

- Reaction score

- 2

- Trophy points

- 1,298

- Location

- Taipei

- Activity points

- 2,810

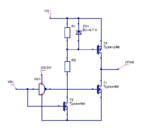

Hi all:

I use a high voltage tech.

The high voltage PMOS/NMOS operation condition:

a. vds : 0~40V

b. vgs : 0~5V

c. VDD is 40V

I need some logic cells to control the circuit,

do you have suggestion for design an inverter?

Thanks for your reply.

mpig

I use a high voltage tech.

The high voltage PMOS/NMOS operation condition:

a. vds : 0~40V

b. vgs : 0~5V

c. VDD is 40V

I need some logic cells to control the circuit,

do you have suggestion for design an inverter?

Thanks for your reply.

mpig