prcken

Advanced Member level 1

Hi,

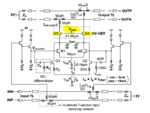

I have a question about how to do bias properly for BJT in CML circuits.

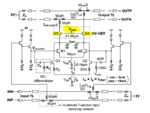

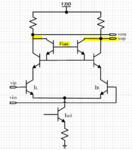

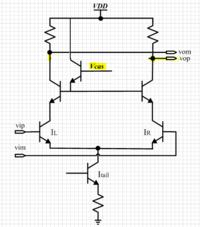

Usually in order to get a large voltage swing the current is really large (e.g. > 10mA), for high speed design, and cascoded device was added for avoiding breakdown (like the picture i attached). However, the base current for the cascoded devices (Q3 and Q4) usually won't be small, so that poses challenge for designing the Vcasc.

Basically, Vcasc drops due the base current!

I don't think just by boosting Vcasc is a good way to solve it. Do you have any comments?

Thanks!

I have a question about how to do bias properly for BJT in CML circuits.

Usually in order to get a large voltage swing the current is really large (e.g. > 10mA), for high speed design, and cascoded device was added for avoiding breakdown (like the picture i attached). However, the base current for the cascoded devices (Q3 and Q4) usually won't be small, so that poses challenge for designing the Vcasc.

Basically, Vcasc drops due the base current!

I don't think just by boosting Vcasc is a good way to solve it. Do you have any comments?

Thanks!