lokesh_boddu

Newbie level 4

Hi friends

i have the following questions. Thanks in advance for answering.

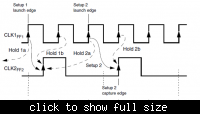

1. How PT calculates setup and hold time between 2 FF clocked by two different clocks?

2. When we use set_max_delay and set_min_delay , the delay calculated by the PT is over ridden, so what will happen to the data path( like will PT add “buf” to it)? How PT ensures the time will not exceeds the limit set using the above commands?

3. Calculate Min clock frequency at which the circuit can function?

Regards

Bdu

i have the following questions. Thanks in advance for answering.

1. How PT calculates setup and hold time between 2 FF clocked by two different clocks?

2. When we use set_max_delay and set_min_delay , the delay calculated by the PT is over ridden, so what will happen to the data path( like will PT add “buf” to it)? How PT ensures the time will not exceeds the limit set using the above commands?

3. Calculate Min clock frequency at which the circuit can function?

Regards

Bdu