Insidious

Newbie level 4

- Joined

- Mar 4, 2014

- Messages

- 6

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1

- Activity points

- 58

Hello, I am trying to build and simulate a Dickson Charge Pump in Cadence Virtuoso for class. I need it to bump 1v to 3v. Should be simple enough but the circuit I built is not wokring correctly.

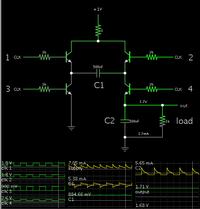

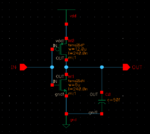

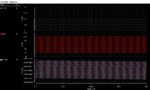

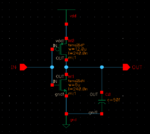

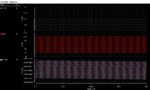

Below are my schematics and output wave forms.

I used the design from wikipedia; I've tried various transistor widths and lengths and also different capcitor values, but I never get more than 1V at the output. My inverter is sized 12/3um (W/L). The clock has a 1ns period and a 500ps pulse width. Not sure what else to try, any pointers?

I don't necessarily need a Disckson charge pump, but it seemed the simplest one to try. Also I cannot use diodes (NCSU libraries don't have diode models), so i must stick to NMOS for the switches.

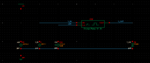

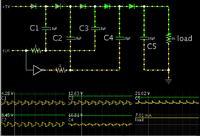

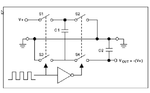

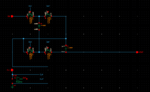

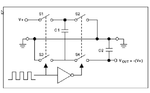

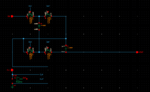

I've also tried this design, even though it is more complicated (from a class slide):

But I just get low voltage at the output.

Any help is appreciated. Thanks in advance.

Below are my schematics and output wave forms.

I used the design from wikipedia; I've tried various transistor widths and lengths and also different capcitor values, but I never get more than 1V at the output. My inverter is sized 12/3um (W/L). The clock has a 1ns period and a 500ps pulse width. Not sure what else to try, any pointers?

I don't necessarily need a Disckson charge pump, but it seemed the simplest one to try. Also I cannot use diodes (NCSU libraries don't have diode models), so i must stick to NMOS for the switches.

I've also tried this design, even though it is more complicated (from a class slide):

But I just get low voltage at the output.

Any help is appreciated. Thanks in advance.