d123

Advanced Member level 5

Hi,

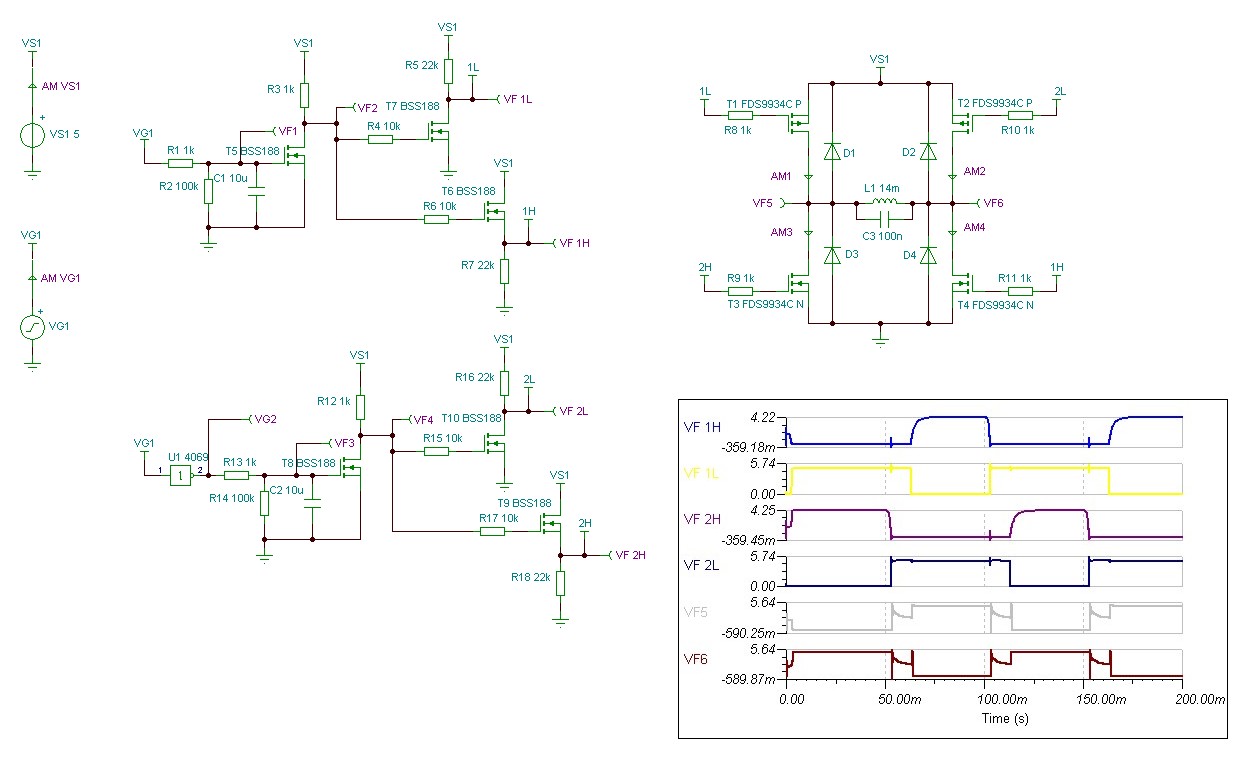

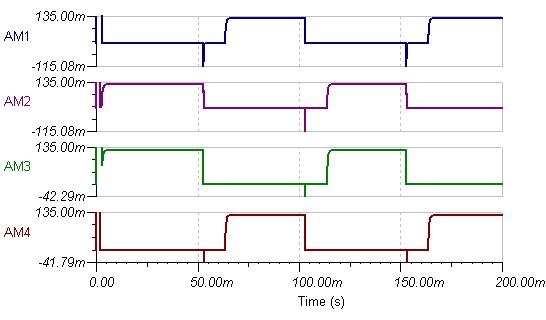

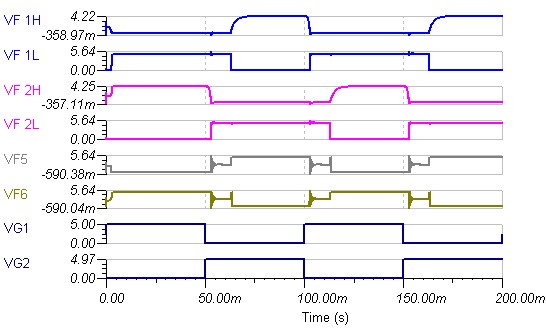

At first glance does anyone recognize what the cause of the horrible h-bridge signals (VF5 and VF6) are being caused by? I put plenty of dead-time in there, as can be seen from the immaculate gate signals, 1H + 1L and 2H + 2L - nothing coincides where it shouldn't and what has to be off is off and what has to be on is on at their expected times. How can there be shoot-through when e.g. T1 and T3 never coincide in being on? I assume it's something obvious and I'm being thick not understanding what I'm being shown by the simulation. Either I can't see something I should by now or I don't understand what ugly 5 and ugly 6 mean here. VG1 is 10 Hz, the inductor has 40 Ohms of resistance, fwiw as information. I'm probably really trying to learn about implementing dead-time and assorted configurations that can achieve that, not making a discrete h-bridge.

Thanks.

At first glance does anyone recognize what the cause of the horrible h-bridge signals (VF5 and VF6) are being caused by? I put plenty of dead-time in there, as can be seen from the immaculate gate signals, 1H + 1L and 2H + 2L - nothing coincides where it shouldn't and what has to be off is off and what has to be on is on at their expected times. How can there be shoot-through when e.g. T1 and T3 never coincide in being on? I assume it's something obvious and I'm being thick not understanding what I'm being shown by the simulation. Either I can't see something I should by now or I don't understand what ugly 5 and ugly 6 mean here. VG1 is 10 Hz, the inductor has 40 Ohms of resistance, fwiw as information. I'm probably really trying to learn about implementing dead-time and assorted configurations that can achieve that, not making a discrete h-bridge.

Thanks.