rishabh_31ec

Member level 1

- Joined

- Sep 13, 2013

- Messages

- 36

- Helped

- 4

- Reputation

- 8

- Reaction score

- 4

- Trophy points

- 1,288

- Activity points

- 1,546

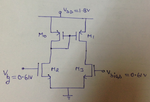

HI, I am designing the current mirror loaded single input differential amplifier using gm/Id vs. Vg and Id/w vs. Vg graph for fixed length of 360nm. I have to use bias voltage at NMOS as 0.61V and gm = 170µs. I have done all calculation by these curve considering Vds2 = 0.8V but after simulation gm and Id both are less than my requirement. What should I do?

circuit is attached in this message.......

circuit is attached in this message.......