FLEXcertifydll

Full Member level 4

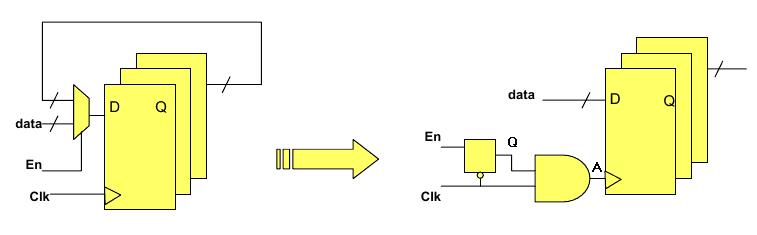

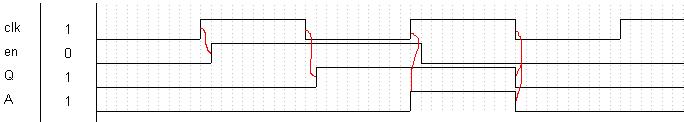

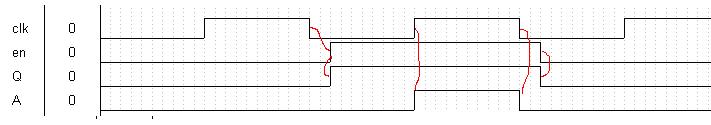

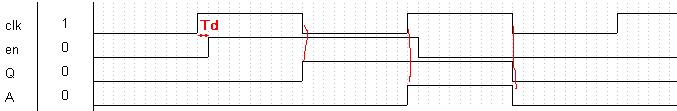

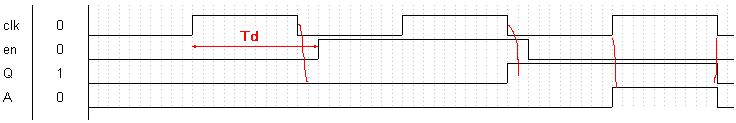

about Gated clock

clock gating is a very common. because the RTL level description is very hard in BE, setup and hold and gated timing check. So vendor will provide the ICG cell for CTS tree, which be balanced, is easy to timing closure.

clock gating is a very common. because the RTL level description is very hard in BE, setup and hold and gated timing check. So vendor will provide the ICG cell for CTS tree, which be balanced, is easy to timing closure.