sabu31

Advanced Member level 1

Dear All,

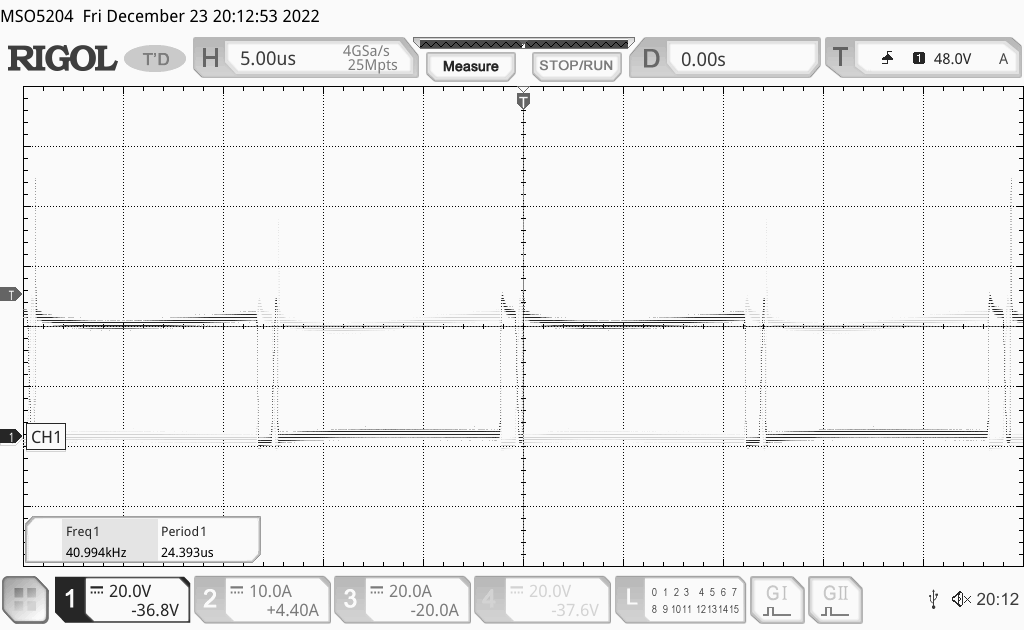

I am testing a prototype of an H-Bridge series parallel resonant inverter. When I am observing the Drain to Source Voltage.

There is some false triggering happening. after the device has turned off. What could be modified in circuit to resolve this issue.

I am testing a prototype of an H-Bridge series parallel resonant inverter. When I am observing the Drain to Source Voltage.

There is some false triggering happening. after the device has turned off. What could be modified in circuit to resolve this issue.