yelstor

Junior Member level 1

I am designing a DC/DC converter.

I chose the fullbridge topology. The requirements are as follows:

Vin = 75 - 125 Vdc Vout = 200V P = 600W Fs = 100 Khz

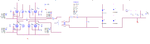

the basic schematic is as follows DC/DC schematic

I use ZVS for soft switching. the problem is the big spike in the Vds on the MOSFETS Vds M2 and M4.

The image above shows the Vds on the down MOSfets and the Vgs for all mosfets. the signal A is the up - left mosfet the signal B is up - right mosfet the signal C is down - left mosfet and the signal D is down - right mosfet

I see that the voltage spike is generated in right leg transition (when D switch is falling)

The same spikes occurs on the primary current I don't know why occurs.

I dont know if the problem is in primary or secondary?.

I provide a large time for discharge the parasitics capacitances (over 400 ns).

Which components oscillate in my design for generate this spikes?

regards and thanks for the answers.

I chose the fullbridge topology. The requirements are as follows:

Vin = 75 - 125 Vdc Vout = 200V P = 600W Fs = 100 Khz

the basic schematic is as follows DC/DC schematic

I use ZVS for soft switching. the problem is the big spike in the Vds on the MOSFETS Vds M2 and M4.

The image above shows the Vds on the down MOSfets and the Vgs for all mosfets. the signal A is the up - left mosfet the signal B is up - right mosfet the signal C is down - left mosfet and the signal D is down - right mosfet

I see that the voltage spike is generated in right leg transition (when D switch is falling)

The same spikes occurs on the primary current I don't know why occurs.

I dont know if the problem is in primary or secondary?.

I provide a large time for discharge the parasitics capacitances (over 400 ns).

Which components oscillate in my design for generate this spikes?

regards and thanks for the answers.