nicoxp31

Newbie level 6

fpgaclk

Hi,

I just wanted to know if they were any danger about multiplexed clock in a FPGA design:

for instance:

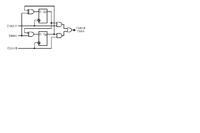

assign clk_o = tx_sel ? tx_clk_i : rx_clk_i;

Can this generate instability then?

Thanks,

Regards,

Jerome

Hi,

I just wanted to know if they were any danger about multiplexed clock in a FPGA design:

for instance:

assign clk_o = tx_sel ? tx_clk_i : rx_clk_i;

Can this generate instability then?

Thanks,

Regards,

Jerome