kathmandu

Full Member level 5

The switching frequency is 16kHz. I've choose a 50Hz transformer because it copes better with overloads (2-3 times the rated power) and I don't have to deal with high voltages.

Follow along with the video below to see how to install our site as a web app on your home screen.

Note: This feature may not be available in some browsers.

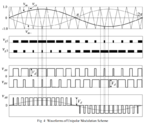

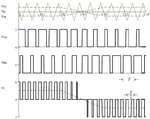

could you post a diagram of how the four gate signals should look like

BTW, the image I've posted above (the unipolar SPWM algorithm) belongs to a Texas Instruments datasheet so I doubt the topology is based on a wrong theory.