MSAKARIM

Full Member level 3

I need help to solve this problem.

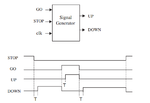

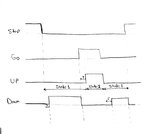

Design a finite state machine capable of generating two signals, UP and DOWN, as illustrated in figure. These signals are controlled by two inputs, GO and STOP.When GO changes from ‘0’ to ‘1’, the output UP must go to ‘1’ too, but T¼10 ms later. If GO returns to ‘0’, then UP must return to ‘0’ immediately. However, the output DOWN must now go to ‘1’, again 10 ms later, returning to ‘0’ immediately if GO changes to ‘1’. If the input STOP is asserted, then both outputs must go to ‘0’ immediately and unconditionally. Assume that a 10 kHz clock is available.

Design a finite state machine capable of generating two signals, UP and DOWN, as illustrated in figure. These signals are controlled by two inputs, GO and STOP.When GO changes from ‘0’ to ‘1’, the output UP must go to ‘1’ too, but T¼10 ms later. If GO returns to ‘0’, then UP must return to ‘0’ immediately. However, the output DOWN must now go to ‘1’, again 10 ms later, returning to ‘0’ immediately if GO changes to ‘1’. If the input STOP is asserted, then both outputs must go to ‘0’ immediately and unconditionally. Assume that a 10 kHz clock is available.