MustafaSami

Newbie

Hello, all.

This is my first post here so I'm sorry if there's any inconvenience.

I'm designing a (very well known) degenerated LNA that contains inductors at both Gate&source of the input core MOS, indicated as LG&LS, respectively.

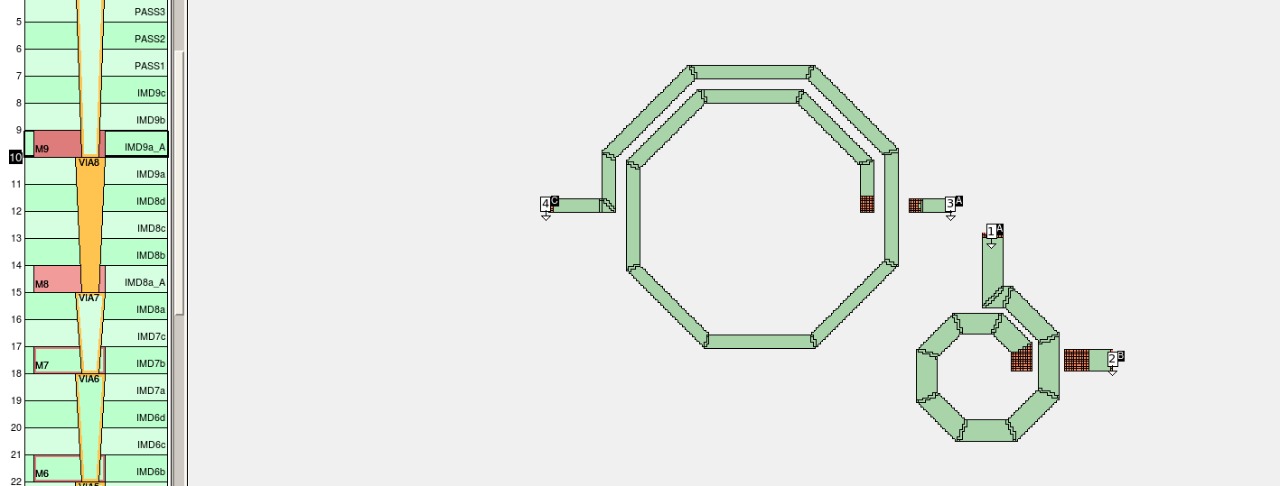

I did layout both inductors in the virtuoso and used sonnet as shown to extract them and successfully managed to generate .s4p file:

Port 1&2 for Ls,

Port 3&4 for Lg.

I was wondering how to simulate them using cadence in order to extract:

Lg, Ls, Q, and mutual inductance between them.

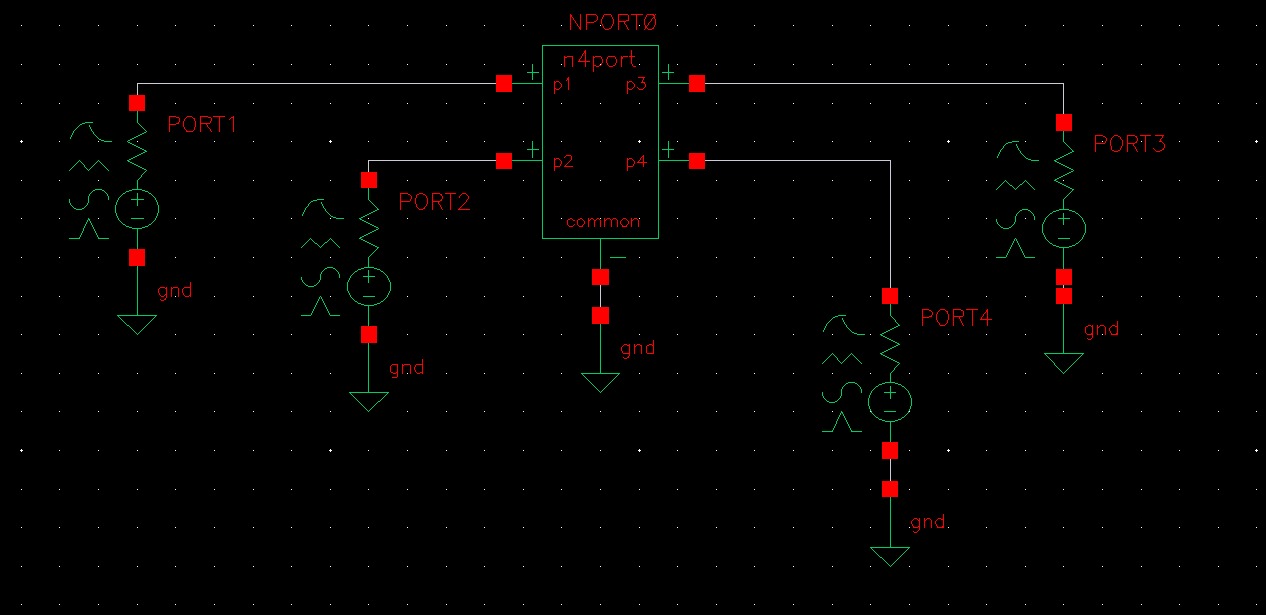

My test bench is shown here.

This is my first post here so I'm sorry if there's any inconvenience.

I'm designing a (very well known) degenerated LNA that contains inductors at both Gate&source of the input core MOS, indicated as LG&LS, respectively.

I did layout both inductors in the virtuoso and used sonnet as shown to extract them and successfully managed to generate .s4p file:

Port 1&2 for Ls,

Port 3&4 for Lg.

I was wondering how to simulate them using cadence in order to extract:

Lg, Ls, Q, and mutual inductance between them.

My test bench is shown here.