keikaku

Newbie

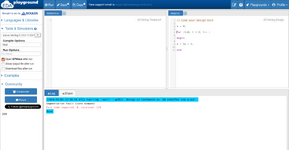

I am brand new to Verilog. I am taking a course. If I am in the wrong place, please let me know.

I am trying to understand how to translate the following C code into Verilog. I just do not get how. Any help is appreciated.

x = 0;

for (i=0; i < 3; i++ ){

x = 2x + 1;

}

Any explanation of how to this can be done ? I suppose this is simple code, but Verilog seems difficult.

I am trying to understand how to translate the following C code into Verilog. I just do not get how. Any help is appreciated.

x = 0;

for (i=0; i < 3; i++ ){

x = 2x + 1;

}

Any explanation of how to this can be done ? I suppose this is simple code, but Verilog seems difficult.