mordak

Member level 5

- Joined

- Mar 8, 2013

- Messages

- 82

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,286

- Location

- Neverland

- Activity points

- 2,134

Hey guys,

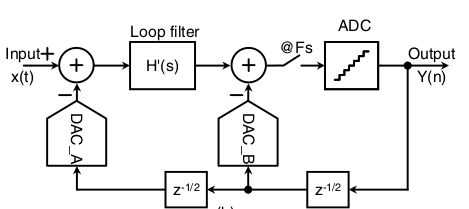

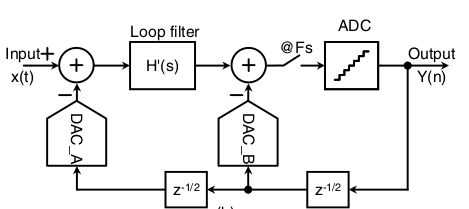

I have a question about continuous time (CT) delta sigma modulators. As you know excess loop delay (ELD) may result in decreasing SNR or even instability. But there is a way to compensate excess loop delay in CT ADCs by adding a second loop and using Dlatch and D flip flops (attached pic). It's from a paper published by Shouli Yan :

A Continuous-Time Delta Sigma Modulator With 88-dB Dynamic Range and 1.1-MHz Signal Bandwidth

I also tried to simulate it in Simulink to see how it works. After simulation I saw that any delay generated by ADC up to 1 clock cycle could be tolerated with this technique. However, still any delay by DAC_A would result in significant SNR degradation of the whole ADC. I don't know if I made a mistake somewhere or it makes sense. Any suggestion would be appreciated.

Thanks

I have a question about continuous time (CT) delta sigma modulators. As you know excess loop delay (ELD) may result in decreasing SNR or even instability. But there is a way to compensate excess loop delay in CT ADCs by adding a second loop and using Dlatch and D flip flops (attached pic). It's from a paper published by Shouli Yan :

A Continuous-Time Delta Sigma Modulator With 88-dB Dynamic Range and 1.1-MHz Signal Bandwidth

I also tried to simulate it in Simulink to see how it works. After simulation I saw that any delay generated by ADC up to 1 clock cycle could be tolerated with this technique. However, still any delay by DAC_A would result in significant SNR degradation of the whole ADC. I don't know if I made a mistake somewhere or it makes sense. Any suggestion would be appreciated.

Thanks