samabraham

Newbie level 6

- Joined

- Mar 16, 2013

- Messages

- 12

- Helped

- 3

- Reputation

- 6

- Reaction score

- 3

- Trophy points

- 1,283

- Location

- Bangalore

- Activity points

- 1,359

Hi All,

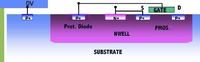

Please suggest me how to connect diodes to avoid Antenna Violation. I referred some books all are explaining it differently, some books suggesting to connect the N(cathode -ntype diffusion) of the diode to metal causing violation and P(anode- p substrate) to GND while some other book suggest to connect P(anode-ptype diffusion) of the diode to the metal causing violation and N(cathode-Nwell) to VDD

Please suggest me how to connect diodes to avoid Antenna Violation. I referred some books all are explaining it differently, some books suggesting to connect the N(cathode -ntype diffusion) of the diode to metal causing violation and P(anode- p substrate) to GND while some other book suggest to connect P(anode-ptype diffusion) of the diode to the metal causing violation and N(cathode-Nwell) to VDD