michcfr

Advanced Member level 4

Hello,

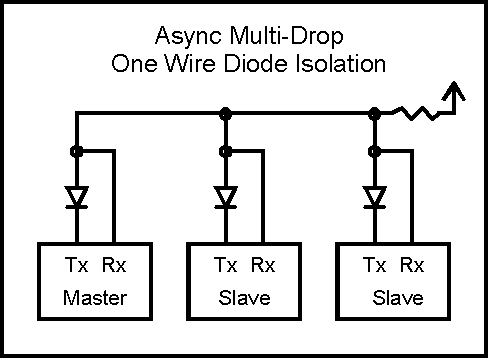

I would like to implement multi-MCU communication with UART sharing like in the picture below.

The MCU ara colocated on the same PCB and at few cm of distance; it is 3.3V logic.

What model of diode (with single or many (4 or 8 diodes) in the same package) and resistor value would you suggest?

thank you

Michel

thank you

Michel

I would like to implement multi-MCU communication with UART sharing like in the picture below.

The MCU ara colocated on the same PCB and at few cm of distance; it is 3.3V logic.

What model of diode (with single or many (4 or 8 diodes) in the same package) and resistor value would you suggest?

thank you

Michel

thank you

Michel