kingssk

Junior Member level 2

Hi,

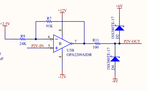

I have designed the waveform clipper Circuit using diode, please find the attachment for my design,

In this my input at P2V-IN is 0-5V square wave and am expecting the output as +6V to -8V square wave output but am getting output as +10.2V to -10.2V could any one please tell me what will be the issue why the clipping is not happening here?

**broken link removed**

I have designed the waveform clipper Circuit using diode, please find the attachment for my design,

In this my input at P2V-IN is 0-5V square wave and am expecting the output as +6V to -8V square wave output but am getting output as +10.2V to -10.2V could any one please tell me what will be the issue why the clipping is not happening here?

**broken link removed**