hanikapa

Member level 4

Hello

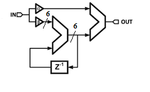

I should implement a proportional- integrator loop filter. in the integral part, there is one accumulator which I implement using full adder as in the picture. there is 6 bits at the inputs of full adder and the output with carry is 7 bit. But it seems that here the carry is ignored, does anybody have experience if I am right? In this case where should we use the carry bit?

I should implement a proportional- integrator loop filter. in the integral part, there is one accumulator which I implement using full adder as in the picture. there is 6 bits at the inputs of full adder and the output with carry is 7 bit. But it seems that here the carry is ignored, does anybody have experience if I am right? In this case where should we use the carry bit?