Dididito

Newbie level 5

Hello everybody,

This is my first post in the forum. I hope I can learn as much as possible from all of you, and help you when you need it.

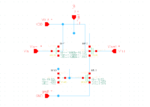

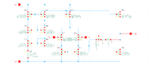

I'm starting right now on IC design, I would like to desing a Two Stages OpAmp. With a differential pair in the first stage.

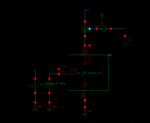

The differential pair I'm using as reference has two PMOS as input and two NMOS as active load. I'm using AMS 0.35um technology.

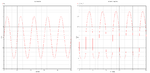

My problem is that the output of the differential pair is saturated, and I really don't know how to solve it. Any idea or advice??

Thank you very much in advance.

This is my first post in the forum. I hope I can learn as much as possible from all of you, and help you when you need it.

I'm starting right now on IC design, I would like to desing a Two Stages OpAmp. With a differential pair in the first stage.

The differential pair I'm using as reference has two PMOS as input and two NMOS as active load. I'm using AMS 0.35um technology.

My problem is that the output of the differential pair is saturated, and I really don't know how to solve it. Any idea or advice??

Thank you very much in advance.