sasi_badveli

Newbie level 6

Hello all,

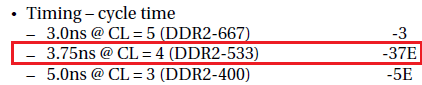

I have few questions regarding CAS Latency. For example,if the DDR2 SDRAM consists of a CAS Latency of 4,and if the DDR2 SDRAM memory controller generated using MIG has a latency of 3? Does the design work together? Any help would be appreciated.

Thanks.

I have few questions regarding CAS Latency. For example,if the DDR2 SDRAM consists of a CAS Latency of 4,and if the DDR2 SDRAM memory controller generated using MIG has a latency of 3? Does the design work together? Any help would be appreciated.

Thanks.