flote21

Advanced Member level 1

- Joined

- Jan 22, 2014

- Messages

- 411

- Helped

- 1

- Reputation

- 2

- Reaction score

- 3

- Trophy points

- 1,298

- Activity points

- 5,595

Hello,

I am having some problems to read the '0' logic values from the DIP Swithches with an ALTERA Cyclone IV FPGA. I always read '1' logic whatever position is configured in the switches

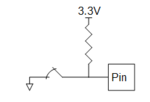

DIP Switches are connected in this way, When they are ON, both sides of the SW are connected to VDD throughr a resistor. Therefore the FPGA read "VDD".

And when they are OFF, the pin of the FPGA is open circuit. I mean there is not any connection to ground through the SW. Simply, the DIP SW open the circuit and leave the FPGA pin without any connection...I measured in the pon of the FPGA and I got 20mV. In theory this should be read like a '0' logic, right? What could be the problem?

Is there any special constraint that I have to add to my pin assgnments file?

Note: I've also tried to connect manually the PIN of the FPGA to GND and then the FPGA read '0'.

Thanks a lot!

I am having some problems to read the '0' logic values from the DIP Swithches with an ALTERA Cyclone IV FPGA. I always read '1' logic whatever position is configured in the switches

DIP Switches are connected in this way, When they are ON, both sides of the SW are connected to VDD throughr a resistor. Therefore the FPGA read "VDD".

And when they are OFF, the pin of the FPGA is open circuit. I mean there is not any connection to ground through the SW. Simply, the DIP SW open the circuit and leave the FPGA pin without any connection...I measured in the pon of the FPGA and I got 20mV. In theory this should be read like a '0' logic, right? What could be the problem?

Is there any special constraint that I have to add to my pin assgnments file?

Note: I've also tried to connect manually the PIN of the FPGA to GND and then the FPGA read '0'.

Thanks a lot!