axcdd

Full Member level 3

- Joined

- Jan 29, 2012

- Messages

- 154

- Helped

- 58

- Reputation

- 116

- Reaction score

- 57

- Trophy points

- 1,308

- Activity points

- 2,133

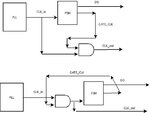

I got 2 example designs and I am wondering how to constraing them correctly.

see attachment

First design:

Signal CLK_in is 120 MHz from PLL. It goes to to FSM module that generates serial data signal DO to external device with 4.3 ns setup and 0 ns hold time referring to clock signal ( CLK_out that has to be gated -- ( gated by signal from FSM register driven by CLK_in signal).

i guess that

is not enought.

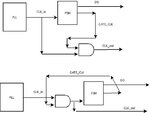

Second design is much worse idea -> clock is gated before FSM.

see attachment

First design:

Signal CLK_in is 120 MHz from PLL. It goes to to FSM module that generates serial data signal DO to external device with 4.3 ns setup and 0 ns hold time referring to clock signal ( CLK_out that has to be gated -- ( gated by signal from FSM register driven by CLK_in signal).

i guess that

Code:

derive_pll_clocks -create_base_clocks

derive_clock_uncertainty

create_generated_clock -name CLK_out -source [get_pins {inst6|pll_inst|altera_pll_i|CLK_in}] [get_ports {CLK_out}]

set_output_delay -clock { CLK_out } -max 4.2 [get_ports {DO}]

set_output_delay -clock { CLK_out } -min 0 [get_ports {DO}]is not enought.

Second design is much worse idea -> clock is gated before FSM.