grittinjames

Advanced Member level 1

- Joined

- Jun 1, 2006

- Messages

- 479

- Helped

- 44

- Reputation

- 90

- Reaction score

- 32

- Trophy points

- 1,308

- Location

- bangalore india

- Activity points

- 3,985

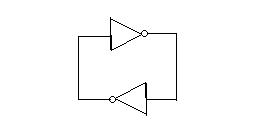

cmos inverter as a saturated amplifier

Hi,

I have a basic doubt, what will happen if I short input and output of cmos inverter

I am getting different answer from many experts like it will oscilates .it will move to lenear region etc .

Any one please give a satisfactory answer

no doubt you will get 10 points

Hi,

I have a basic doubt, what will happen if I short input and output of cmos inverter

I am getting different answer from many experts like it will oscilates .it will move to lenear region etc .

Any one please give a satisfactory answer

no doubt you will get 10 points