vinodkumar

Full Member level 5

dear all,

iam looking for a verilog code :

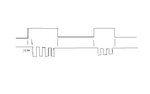

in which the input control signal is a signal with pulse width of 1us and period of 10us,

output signal should be logic 1 when control is zero and

40MHz clock when control signal is logic1 and clk should be assigned after 12.5ns of logic1 .

attached figure :

module(clk,control,latch_en);

input clk;//40MHz

input control;

output latch_en;

iam looking for a verilog code :

in which the input control signal is a signal with pulse width of 1us and period of 10us,

output signal should be logic 1 when control is zero and

40MHz clock when control signal is logic1 and clk should be assigned after 12.5ns of logic1 .

attached figure :

module(clk,control,latch_en);

input clk;//40MHz

input control;

output latch_en;