zopeon

Member level 2

Hello everyone,

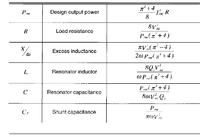

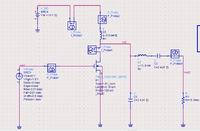

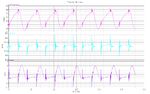

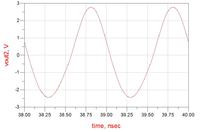

I have to design a class E output stage for Pout= 8mW (targeted for zigbee type apps ) with fc = 2.45Ghz using UMC 180nm RFCMOS technology. I have gone through RF books by Lee and Crips and through Sokal et all Class E paper. but when I designed it and ran transient analysis I get the On-state voltage closer to the Vdd (1V) what am I doing wrong?

Also could you guide me any other material to help me in my design?

other doubts are

Ropt value for this comes greater than 50 is it correct??

Selection of MOSFET size as it is to be used as a switch?

I am using cadence spectre for simulation

Thanks & Regards

I have to design a class E output stage for Pout= 8mW (targeted for zigbee type apps ) with fc = 2.45Ghz using UMC 180nm RFCMOS technology. I have gone through RF books by Lee and Crips and through Sokal et all Class E paper. but when I designed it and ran transient analysis I get the On-state voltage closer to the Vdd (1V) what am I doing wrong?

Also could you guide me any other material to help me in my design?

other doubts are

Ropt value for this comes greater than 50 is it correct??

Selection of MOSFET size as it is to be used as a switch?

I am using cadence spectre for simulation

Thanks & Regards