shockingshockley

Member level 1

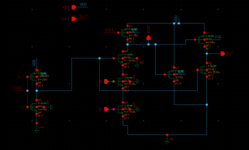

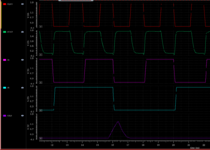

Hello. I am working for a circuit to generate 2 non-overlapping clocks in GHz range. However, the circuit only works in the MHz range. What are the probable reasons why it does not work? Or do you have any suggested circuit for this purpose? TIA