crazyfox

Junior Member level 2

HI :

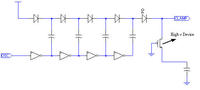

I have a charge pump circuit like Fig. , from the simulation result it can pump up

to the 12v , but in real measurement, i find the block cannot pump to the high

voltage. The question is it really hard to find the bug on the wafer, anyone who

have ever design the charge pump, can give me some suggestion from your

experience, which place that i might not concern. Any way could i find the

problem of the circuit on the wafer.

One that i can think is the HV device have leakage current, and the other is the

diode device might have problem, layout? or model? how to verification ?

Thanks for your read and give me suggestion

I have a charge pump circuit like Fig. , from the simulation result it can pump up

to the 12v , but in real measurement, i find the block cannot pump to the high

voltage. The question is it really hard to find the bug on the wafer, anyone who

have ever design the charge pump, can give me some suggestion from your

experience, which place that i might not concern. Any way could i find the

problem of the circuit on the wafer.

One that i can think is the HV device have leakage current, and the other is the

diode device might have problem, layout? or model? how to verification ?

Thanks for your read and give me suggestion