yefj

Advanced Member level 5

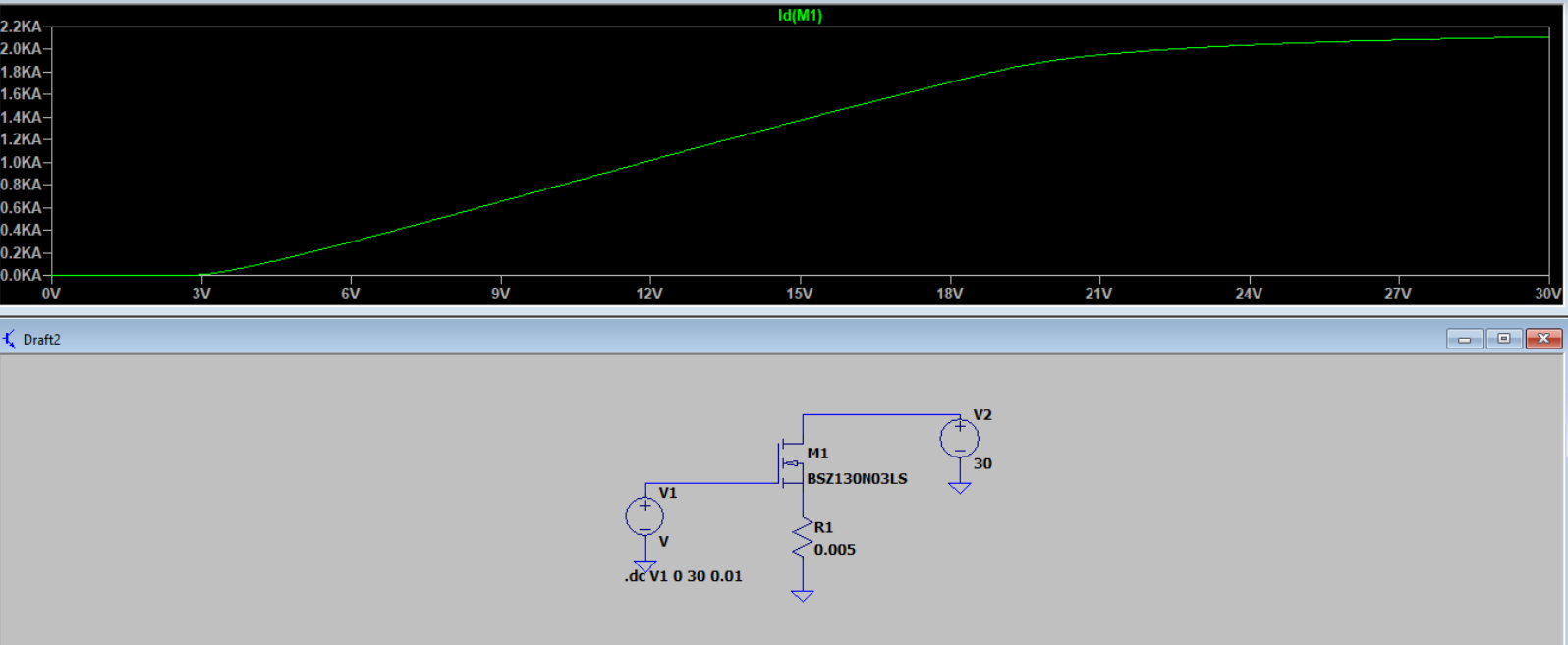

Hello,i am trying to simulate the lecture circuit shown bellow and i do get the effect shown in the lecture ,i dont understand why saturation point is moving.

we have a bias current so our source point increased.

So i expect the Vgs>Vt threshhold voltage to move also ,because we need to put Vg=Vt+Id*Rs to get the transistor opened .

but as you can see in the simulation bellow it stayed steady.

Why is that?

also why the saturation point is moving mathematickly speaking? and why putting mosfet instead of Rs solves this problem?

Thanks.

we have a bias current so our source point increased.

So i expect the Vgs>Vt threshhold voltage to move also ,because we need to put Vg=Vt+Id*Rs to get the transistor opened .

but as you can see in the simulation bellow it stayed steady.

Why is that?

also why the saturation point is moving mathematickly speaking? and why putting mosfet instead of Rs solves this problem?

Thanks.