johnnyG1995

Newbie level 1

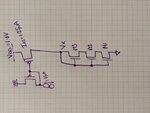

Hello, I'm trying to build a bias circuit for a cascode stage. My prof suggested the circuit attached but I can't figure a way to work out Vx.

I know I have a PMOS current mirror at the top so that means the current is set to 1.25uA. I know the NMOS must be self biasing - or at least M3 must be because of the common gate/drain connection. But the addition of M1 and M2 leave me stuck.

I thought about rearranging the Ids equation, but the equation for saturation region doesn't contain a Vds (assuming no short channel effects). And that's whats I'm looking for really right?

Vx = VdsM1+VdsM2+VdsM3

Any help would be appreciated.

I know I have a PMOS current mirror at the top so that means the current is set to 1.25uA. I know the NMOS must be self biasing - or at least M3 must be because of the common gate/drain connection. But the addition of M1 and M2 leave me stuck.

I thought about rearranging the Ids equation, but the equation for saturation region doesn't contain a Vds (assuming no short channel effects). And that's whats I'm looking for really right?

Vx = VdsM1+VdsM2+VdsM3

Any help would be appreciated.