ravi2024

Newbie level 6

Hi,

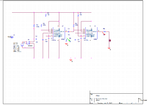

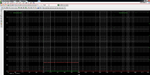

I was trying to simulate a cascaded double stage 555 timer IC ckt. The motto was to get two voltage o/p displaced in time. But the voltage pulse at second stage output is vary less. I am using a 10 V battery as the source and the first output voltage pulse is around 9.6 V but the output voltage pulse is only 1.4 volts. Could anyone tell me why so or where is the fault? I have attached the ckt and the output plot.

I was trying to simulate a cascaded double stage 555 timer IC ckt. The motto was to get two voltage o/p displaced in time. But the voltage pulse at second stage output is vary less. I am using a 10 V battery as the source and the first output voltage pulse is around 9.6 V but the output voltage pulse is only 1.4 volts. Could anyone tell me why so or where is the fault? I have attached the ckt and the output plot.