yassin.kraouch

Advanced Member level 2

- Joined

- Jul 5, 2009

- Messages

- 631

- Helped

- 40

- Reputation

- 80

- Reaction score

- 40

- Trophy points

- 1,308

- Activity points

- 5,094

Hi,

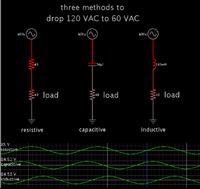

can anyone explain to me the capacitive drop drive topology ? how it works ? what is the role of the capacitor ?

thanks,

can anyone explain to me the capacitive drop drive topology ? how it works ? what is the role of the capacitor ?

thanks,