tok47

Advanced Member level 4

- Joined

- Jan 16, 2004

- Messages

- 119

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,296

- Location

- Kuala Lumpur, MALAYSIA

- Activity points

- 1,013

Hi ALL,

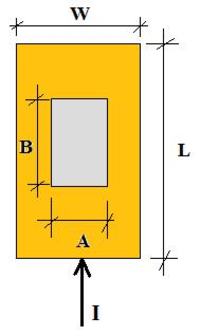

I had a metal layer of bus signal which i wish to calculate the effective resistance of this layer.

Please see the attachment file for the layout.

Can i just calculate the whole rectangle and minus the the empty space to get the effective resistance? will it be accurate?

Thanks.

Rdgs

YY

p/s : {[(X * Y) - (area of the empty space)] * sheet resistance }= effective resistance

I had a metal layer of bus signal which i wish to calculate the effective resistance of this layer.

Please see the attachment file for the layout.

Can i just calculate the whole rectangle and minus the the empty space to get the effective resistance? will it be accurate?

Thanks.

Rdgs

YY

p/s : {[(X * Y) - (area of the empty space)] * sheet resistance }= effective resistance