Mustafatarhan49

Junior Member level 2

Hello guys,

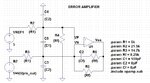

I wanna know how the designer calculated the below error amplifier circuit component values in the attached figure. Can anyone help me to figure out how to calculate this compensation values?

And I also wanna know which type of compensation network is this. I will appriciate if you can help me!

Thanks a lot!

Regards,

I wanna know how the designer calculated the below error amplifier circuit component values in the attached figure. Can anyone help me to figure out how to calculate this compensation values?

And I also wanna know which type of compensation network is this. I will appriciate if you can help me!

Thanks a lot!

Regards,