cupoftea

Advanced Member level 5

Hi,

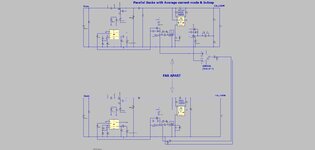

Do you agree the attached (LTspice and jpeg), is the best way to parallel SMPS?

The Voltage error amp signal is passed to the other SMPS's via an AD8226 (X1 Gain) InAmp.....this means that even if the local ground potential at each Buck is different, each buck will still receive the same signal to its current error amplifier (due to the InAmp)

AD8226

Do you agree the attached (LTspice and jpeg), is the best way to parallel SMPS?

The Voltage error amp signal is passed to the other SMPS's via an AD8226 (X1 Gain) InAmp.....this means that even if the local ground potential at each Buck is different, each buck will still receive the same signal to its current error amplifier (due to the InAmp)

AD8226