Div_01

Newbie level 4

Hi,

I have a question regarding addition in digital electronics, quite application specific.

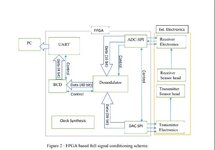

1)Let's say, I have 2 16-bit data coming from DAC and ADC to the demodulator that is 32 bits after multiplying. How many times is addition done to obtain a 40 bit data?

2) What would be the demodulator clock period for a 50MHz internal clock frequency and 32KHz sine wave? The answer that is obtained is 1320 as the demodulator clock period. But I am unable to understand how that number is obtained.

Please let me know if more details are required.

Can anyone explain me the procedure as well?

Thanks,

Divya

I have a question regarding addition in digital electronics, quite application specific.

1)Let's say, I have 2 16-bit data coming from DAC and ADC to the demodulator that is 32 bits after multiplying. How many times is addition done to obtain a 40 bit data?

2) What would be the demodulator clock period for a 50MHz internal clock frequency and 32KHz sine wave? The answer that is obtained is 1320 as the demodulator clock period. But I am unable to understand how that number is obtained.

Please let me know if more details are required.

Can anyone explain me the procedure as well?

Thanks,

Divya

Last edited: