GreatField

Newbie level 6

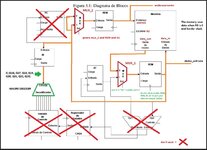

My code compiles perfectly in quartus II, but when simulating in the waveform it seems that the components are not being used because nothing happens in the simulation.

See my RTL Viewer:

See my code:

See my RTL Viewer:

See my code:

Code:

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE IEEE.numeric_std.all;

LIBRARY work;

ENTITY Projeto IS

PORT

(

--GND : IN STD_LOGIC;

dados_entrada : INOUT unsigned (7 downto 0);

enderecamento : INOUT unsigned (3 downto 0);

dados_de_saida : INOUT unsigned (7 downto 0);

leitura : INOUT std_logic;

Clock_mem : INOUT std_logic;

Clock_reg_RDM : INOUT std_logic;

Clock_reg_RI : INOUT std_logic;

bit_selector_mux1 : INOUT std_logic;

saida_reg_RI : INOUT unsigned (7 downto 0)

);

END Projeto;

ARCHITECTURE top_lvl_entity OF Projeto IS

COMPONENT registrador_REM IS

PORT

(

CLOCK, D0, D1, D2, D3, D4, D5, D6, D7 : INOUT STD_LOGIC;

Q0, Q1, Q2, Q3, Q4, Q5, Q6, Q7 : BUFFER STD_LOGIC

);

END COMPONENT registrador_REM;

COMPONENT registrador_RDM IS

PORT

(

CLK, D8, D9, D10, D11, D12, D13, D14, D15 : INOUT STD_LOGIC;

Q8, Q9, Q10, Q11, Q12, Q13, Q14, Q15 : BUFFER STD_LOGIC

);

END COMPONENT registrador_RDM;

COMPONENT registrador_RI IS

PORT

(

C_L_K, D16, D17, D18, D19, D20, D21, D22, D23 : INOUT STD_LOGIC;

Q16, Q17, Q18, Q19, Q20, Q21, Q22, Q23 : BUFFER STD_LOGIC

);

END COMPONENT registrador_RI;

COMPONENT registrador_AC IS

PORT

(

C_L_O_C_K, D24, D25, D26, D27, D28, D29, D30, D31 : INOUT STD_LOGIC;

Q24, Q25, Q26, Q27, Q28, Q29, Q30, Q31 : BUFFER STD_LOGIC

);

END COMPONENT registrador_AC;

COMPONENT mux_1 IS

PORT

(

A0 : INOUT STD_LOGIC;

B0 : INOUT STD_LOGIC;

A1 : INOUT STD_LOGIC;

B1 : INOUT STD_LOGIC;

A2 : INOUT STD_LOGIC;

B2 : INOUT STD_LOGIC;

A3 : INOUT STD_LOGIC;

B3 : INOUT STD_LOGIC;

A4 : INOUT STD_LOGIC;

B4 : INOUT STD_LOGIC;

A5 : INOUT STD_LOGIC;

B5 : INOUT STD_LOGIC;

A6 : INOUT STD_LOGIC;

B6 : INOUT STD_LOGIC;

A7 : INOUT STD_LOGIC;

B7 : INOUT STD_LOGIC;

bit_controle : INOUT STD_LOGIC;

S1 : INOUT STD_LOGIC;

S2 : INOUT STD_LOGIC;

S3 : INOUT STD_LOGIC;

S4 : INOUT STD_LOGIC;

S5 : INOUT STD_LOGIC;

S6 : INOUT STD_LOGIC;

S7 : INOUT STD_LOGIC;

S8 : INOUT STD_LOGIC

);

END COMPONENT mux_1;

COMPONENT mux_2 IS

PORT

(

C0 : INOUT STD_LOGIC;

F0 : INOUT STD_LOGIC;

C1 : INOUT STD_LOGIC;

F1 : INOUT STD_LOGIC;

C2 : INOUT STD_LOGIC;

F2 : INOUT STD_LOGIC;

C3 : INOUT STD_LOGIC;

F3 : INOUT STD_LOGIC;

C4 : INOUT STD_LOGIC;

F4 : INOUT STD_LOGIC;

C5 : INOUT STD_LOGIC;

F5 : INOUT STD_LOGIC;

C6 : INOUT STD_LOGIC;

F6 : INOUT STD_LOGIC;

C7 : INOUT STD_LOGIC;

F7 : INOUT STD_LOGIC;

bit_ctrl : INOUT STD_LOGIC;

G1 : INOUT STD_LOGIC;

G2 : INOUT STD_LOGIC;

G3 : INOUT STD_LOGIC;

G4 : INOUT STD_LOGIC;

G5 : INOUT STD_LOGIC;

G6 : INOUT STD_LOGIC;

G7 : INOUT STD_LOGIC;

G8 : INOUT STD_LOGIC

);

END COMPONENT mux_2;

COMPONENT decoder_4x8 IS

PORT

(

B : INOUT STD_LOGIC;

A : INOUT STD_LOGIC;

C : INOUT STD_LOGIC;

D : INOUT STD_LOGIC;

O1 : INOUT STD_LOGIC;

O2 : INOUT STD_LOGIC;

O3 : INOUT STD_LOGIC;

O4 : INOUT STD_LOGIC;

O5 : INOUT STD_LOGIC;

O6 : INOUT STD_LOGIC;

O7 : INOUT STD_LOGIC;

O8 : INOUT STD_LOGIC

);

END COMPONENT decoder_4x8;

COMPONENT memoria_16x8 IS

PORT

(

address : INOUT unsigned (3 downto 0);

data_in : INOUT unsigned (7 downto 0);

data_out : INOUT unsigned (7 downto 0);

RD : INOUT std_logic;

CS : INOUT std_logic

);

END COMPONENT memoria_16x8;

-- SIGNALS

signal t1 : std_logic;

signal t2 : std_logic;

signal t3 : std_logic;

signal t4 : std_logic;

signal t5 : std_logic;

signal t6 : std_logic;

signal t7 : std_logic;

signal t8 : std_logic;

signal t9 : std_logic;

signal t10 : std_logic;

signal t11 : std_logic;

signal t12 : std_logic;

signal t13 : std_logic;

signal t14 : std_logic;

signal t15 : std_logic;

signal t16 : std_logic;

signal t17 : std_logic;

signal t18 : std_logic;

signal t19 : std_logic;

signal t20 : std_logic;

signal t21 : std_logic;

signal t22 : std_logic;

signal t23 : std_logic;

signal t24 : std_logic;

signal t25 : std_logic;

signal t26 : std_logic;

signal t27 : std_logic;

signal t28 : std_logic;

signal t29 : std_logic;

signal t30 : std_logic;

signal t31 : std_logic;

signal t32 : std_logic;

signal t33 : std_logic;

signal t34 : std_logic;

signal t35 : std_logic;

signal t36 : std_logic;

signal t37 : std_logic;

signal t38 : std_logic;

signal t39 : std_logic;

signal t40 : std_logic;

signal t41 : std_logic;

signal t42 : std_logic;

signal t43 : std_logic;

signal t44 : std_logic;

signal t45 : std_logic;

signal t46 : std_logic;

signal t47 : std_logic;

signal t48 : std_logic;

signal t49 : std_logic;

signal t50 : std_logic;

signal t51 : std_logic;

signal t52 : std_logic;

BEGIN

t25 <= dados_entrada(0);

t25 <= dados_entrada(1);

t25 <= dados_entrada(2);

t25 <= dados_entrada(3);

t25 <= dados_entrada(4);

t25 <= dados_entrada(5);

t25 <= dados_entrada(6);

t25 <= dados_entrada(7);

t41 <= enderecamento(0);

t42 <= enderecamento(1);

t43 <= enderecamento(2);

t44 <= enderecamento(3);

t1 <= dados_de_saida(0);

t2 <= dados_de_saida(1);

t3 <= dados_de_saida(2);

t4 <= dados_de_saida(3);

t5 <= dados_de_saida(4);

t6 <= dados_de_saida(5);

t7 <= dados_de_saida(6);

t8 <= dados_de_saida(7);

t45 <= saida_reg_RI(0);

t46 <= saida_reg_RI(1);

t47 <= saida_reg_RI(2);

t48 <= saida_reg_RI(3);

t49 <= saida_reg_RI(4);

t50 <= saida_reg_RI(5);

t51 <= saida_reg_RI(6);

t52 <= saida_reg_RI(7);

P1: memoria_16x8

port map(

--SIGNALS

address(0) => t41,

address(1) => t42,

address(2) => t43,

address(3) => t44,

data_out(0) => t1,

data_out(1) => t2,

data_out(2) => t3,

data_out(3) => t4,

data_out(4) => t5,

data_out(5) => t6,

data_out(6) => t7,

data_out(7) => t8,

data_in(0) => t25,

data_in(1) => t26,

data_in(2) => t27,

data_in(3) => t28,

data_in(4) => t29,

data_in(5) => t30,

data_in(6) => t31,

data_in(7) => t32,

CS => Clock_mem,

RD => leitura

);

P2: registrador_AC

port map(

Q24 => t9,

Q25 => t10,

Q26 => t11,

Q27 => t12,

Q28 => t13,

Q29 => t14,

Q30 => t15,

Q31 => t16

);

P3: mux_1

port map(

-- SIGNALS

A0 => t1,

B0 => t2,

A1 => t3,

B1 => t4,

A2 => t5,

B2 => t6,

A3 => t7,

B3 => t8,

A4 => t9,

B4 => t10,

A5 => t11,

B5 => t12,

A6 => t13,

B6 => t14,

A7 => t15,

B7 => t16,

S1 => t17,

S2 => t18,

S3 => t19,

S4 => t20,

S5 => t21,

S6 => t22,

S7 => t23,

S8 => t24,

bit_controle => bit_selector_mux1

);

P4: registrador_RDM

port map(

--SIGNALS

D8 => t17,

D9 => t18,

D10 => t19,

D11 => t20,

D12 => t21,

D13 => t22,

D14 => t23,

D15 => t24,

Q8 => t25,

Q9 => t26,

Q10 => t27,

Q11 => t28,

Q12 => t29,

Q13 => t30,

Q14 => t31,

Q15 => t32,

CLK => Clock_reg_RDM

);

P8: mux_2

port map(

--SIGNALS

C0 => t25,

F0 => t26,

C1 => t27,

F1 => t28,

C2 => t29,

F2 => t30,

C3 => t31,

F3 => t32,

C4 => t25,

F4 => t26,

C5 => t27,

F5 => t28,

C6 => t29,

F6 => t30,

C7 => t31,

F7 => t32,

G1 => t33,

G2 => t34,

G3 => t35,

G4 => t36,

G5 => t37,

G6 => t38,

G7 => t39,

G8 => t40

);

P9: registrador_REM

port map(

--SIGNALS

D0 => t33,

D1 => t34,

D2 => t35,

D3 => t36,

D4 => t37,

D5 => t38,

D6 => t39,

D7 => t40,

Q0 => t41,

Q1 => t42,

Q2 => t43,

Q3 => t44

);

P10: registrador_RI

port map(

Q16 => t45,

Q17 => t46,

Q18 => t47,

Q19 => t48,

Q20 => t49,

Q21 => t50,

Q22 => t51,

Q23 => t52,

D16 => t25,

D17 => t26,

D18 => t27,

D19 => t28,

D20 => t29,

D21 => t30,

D22 => t31,

D23 => t32,

C_L_K => Clock_reg_RI

);

P11: decoder_4x8

port map(

--SIGNALS

A => t45,

B => t46,

C => t47,

D => t48

);

END top_lvl_entity;

Last edited by a moderator: