TnF

Junior Member level 3

- Joined

- Mar 1, 2015

- Messages

- 31

- Helped

- 1

- Reputation

- 2

- Reaction score

- 1

- Trophy points

- 8

- Activity points

- 350

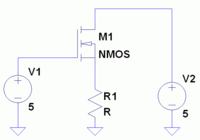

Hello guys. I'm new to electronic design, but i just got into simulation. So to keep the question short basically i localized my problem to a specific component i use in Altium designer. It's an IRL2203N mosfet. Because i did try several things with no avail i just made a simple schematic and the problem now is very clear. I get a 2.35V drop across VDS. VGS is 5V, same as my VDS. My load is connected to the source (even though ideally you want to connect it in the drain - i'll test that way in a bit if it makes any difference). I know that i will have a small voltage drop across but look at the datasheet MAX 10mohm at VGS=4.5V. I'm not even doing any high frequency switching. Signal is a 4ms pulsewidth, >100hz pulse. Altium uses the following Spice model:

What is going on? Is it because of the model file?

Kind regards,

Ken

Code:

**************************************

* Model Generated by MODPEX *

*Copyright(c) Symmetry Design Systems*

* All Rights Reserved *

* UNPUBLISHED LICENSED SOFTWARE *

* Contains Proprietary Information *

* Which is The Property of *

* SYMMETRY OR ITS LICENSORS *

*Commercial Use or Resale Restricted *

* by Symmetry License Agreement *

**************************************

* Model generated on Sep 27, 01

* MODEL FORMAT: SPICE3

* Symmetry POWER MOS Model (Version 1.0)

* External Node Designations

* Node 1 -> Drain

* Node 2 -> Gate

* Node 3 -> Source

.SUBCKT irl2203n 1 2 3

M1 9 7 8 8 MM L=100u W=100u

.MODEL MM NMOS (LEVEL=1 IS=1e-32

+VTO=2.36103 LAMBDA=0.0325968 KP=204.753

+CGSO=3.1e-05 CGDO=1e-11)

RS 8 3 0.00427452

D1 3 1 MD

.MODEL MD D (IS=8.56401e-11 RS=0.00355838 N=1.14431 BV=30

+IBV=0.00025 EG=1 XTI=1 TT=0

+CJO=4e-09 VJ=1.16989 M=0.419864 FC=0.5)

RDS 3 1 1e+06

RD 9 1 0.0001

RG 2 7 6

D2 4 5 MD1

* Default values used in MD1:

* RS=0 EG=1.11 XTI=3.0 TT=0

* BV=infinite IBV=1mA

.MODEL MD1 D (IS=1e-32 N=50

+CJO=1.87864e-09 VJ=1.71885 M=0.867625 FC=1e-08)

D3 0 5 MD2

* Default values used in MD2:

* EG=1.11 XTI=3.0 TT=0 CJO=0

* BV=infinite IBV=1mA

.MODEL MD2 D (IS=1e-10 N=0.4 RS=3e-06)

RL 5 10 1

FI2 7 9 VFI2 -1

VFI2 4 0 0

EV16 10 0 9 7 1

CAP 11 10 3.38961e-09

FI1 7 9 VFI1 -1

VFI1 11 6 0

RCAP 6 10 1

D4 0 6 MD3

* Default values used in MD3:

* EG=1.11 XTI=3.0 TT=0 CJO=0

* RS=0 BV=infinite IBV=1mA

.MODEL MD3 D (IS=1e-10 N=0.4)

.ENDS irl2203nWhat is going on? Is it because of the model file?

Kind regards,

Ken