tia_design

Advanced Member level 4

snapback voltage

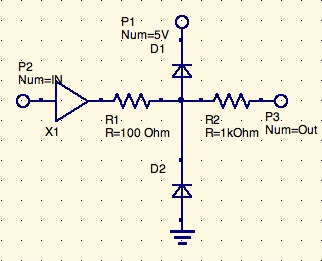

In the process specification, the NMOS breakdown voltage is 7V. Testing case is that NMOS length is 0.6uM, gate, source and substrate are connected to ground, then sweep drain voltage till drain take 1uA current. Process supply is 5V

In my design, I have to take care of protection if op amp's output is accidentally connected to 16V or -6V. If I use NMOS with length of 1.2uM will the breakdown voltage be doubled? Normally how should I do in my design to take care above mentiion 16V and -6V cases. Thanks!

In the process specification, the NMOS breakdown voltage is 7V. Testing case is that NMOS length is 0.6uM, gate, source and substrate are connected to ground, then sweep drain voltage till drain take 1uA current. Process supply is 5V

In my design, I have to take care of protection if op amp's output is accidentally connected to 16V or -6V. If I use NMOS with length of 1.2uM will the breakdown voltage be doubled? Normally how should I do in my design to take care above mentiion 16V and -6V cases. Thanks!