a7m3d

Newbie level 3

How to implement/design 4 phases non-overlapping clock generator?

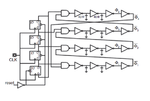

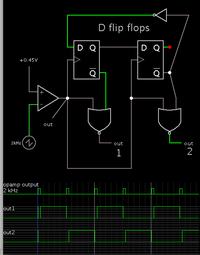

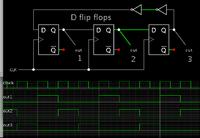

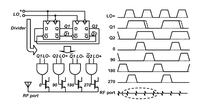

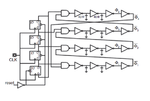

I found this figure without enough details about the implementation. I need a clear reference to build the 4 phases non-overlapping clock generator or in general n phases non-overlapping clock generators for example a 3 phases non-overlapping clock generator.

I found this figure without enough details about the implementation. I need a clear reference to build the 4 phases non-overlapping clock generator or in general n phases non-overlapping clock generators for example a 3 phases non-overlapping clock generator.