T

treez

Guest

Hello,

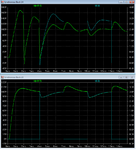

The attached bode plots of gain and phase of a Synchronous Buck Converter show that it has a crossover frequency of 3200 Hz, and a phase margin of just 9 degrees

Surely this cannot be possible?

The LTspice simulation of this Synchronous Buck shows ringing after transients of around 500Hz, so the crossover frequency surely cannot be anywhere near 3200Hz?

Also, the LTspice simulation is stable with minimal, highly damped ringing after transients, so how can its phase margin be just 9 degrees?

The Power stage transfer function of this Synchronous Buck converter was calculated from equation 2A-14 of page 230 of Basso’s book “Switch Mode Power Supplies”

LTspice sim and pdf schem attached (also the bode plots, and Basso’s Page 230).

(there is no mistake in my working, I did the gain phase calculations twice and got the same result each time)

The attached bode plots of gain and phase of a Synchronous Buck Converter show that it has a crossover frequency of 3200 Hz, and a phase margin of just 9 degrees

Surely this cannot be possible?

The LTspice simulation of this Synchronous Buck shows ringing after transients of around 500Hz, so the crossover frequency surely cannot be anywhere near 3200Hz?

Also, the LTspice simulation is stable with minimal, highly damped ringing after transients, so how can its phase margin be just 9 degrees?

The Power stage transfer function of this Synchronous Buck converter was calculated from equation 2A-14 of page 230 of Basso’s book “Switch Mode Power Supplies”

LTspice sim and pdf schem attached (also the bode plots, and Basso’s Page 230).

(there is no mistake in my working, I did the gain phase calculations twice and got the same result each time)