zqbeijing

Newbie level 5

Hello! I'm a newbie on this forum.

I'm currently desinging a h bridge circuit based on a larger scale energy harvester project. Unfortunately, I'm now stucking on the schematic design by using pspice simulation.

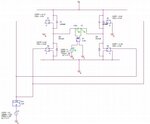

The circuit is actually a quite simple h bridge by using ideal switches as the picture shown in the attachment.

G1 is the voltage controled current source with a sin wave V1 connected to it and drives a voltage difference Vc1 at the output end.

Ideal switches S1-S4 are being used to switch this configuration. The on/off voltages are controled by a sin wave V2 with amplitude equals to 10V and same frequency as the input source to G1. However, I use a limiter to limit this 10V sin wave to +/- 0.4V and make it act as a square wave so the switches can employ.

Therefore, the basic idea of operation should be as following:

1) When V1 reach to a positive peak, V2 also reach to positive peak because they are in same frequency.

2) The square wave reaches to +0.4V simultaneously (no delay at limiter) and this voltage feed in to S1 and S4.

3) S1 and S4 switch on and output of G1 will conduct left to right and the voltage difference Vc1 should be in phase with input V1 because all these should happen at the same time.

4) S1 and S4 switch off and S2/3 switch on, circuit operates in a similar way with another direction.

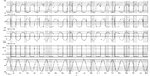

However, the simulation result (also shown in the attachment) is not what I've expected, the waveform of Vc1 has 180 phase shift with V1. I also measured the output voltage from s1 and s2 and they are in different phase as well so I'm sure they won't switch on/off at the same time.

So can any one point out the problem with this design please? I know this might sound retarded, but please help.

Thanks a lot!

I'm currently desinging a h bridge circuit based on a larger scale energy harvester project. Unfortunately, I'm now stucking on the schematic design by using pspice simulation.

The circuit is actually a quite simple h bridge by using ideal switches as the picture shown in the attachment.

G1 is the voltage controled current source with a sin wave V1 connected to it and drives a voltage difference Vc1 at the output end.

Ideal switches S1-S4 are being used to switch this configuration. The on/off voltages are controled by a sin wave V2 with amplitude equals to 10V and same frequency as the input source to G1. However, I use a limiter to limit this 10V sin wave to +/- 0.4V and make it act as a square wave so the switches can employ.

Therefore, the basic idea of operation should be as following:

1) When V1 reach to a positive peak, V2 also reach to positive peak because they are in same frequency.

2) The square wave reaches to +0.4V simultaneously (no delay at limiter) and this voltage feed in to S1 and S4.

3) S1 and S4 switch on and output of G1 will conduct left to right and the voltage difference Vc1 should be in phase with input V1 because all these should happen at the same time.

4) S1 and S4 switch off and S2/3 switch on, circuit operates in a similar way with another direction.

However, the simulation result (also shown in the attachment) is not what I've expected, the waveform of Vc1 has 180 phase shift with V1. I also measured the output voltage from s1 and s2 and they are in different phase as well so I'm sure they won't switch on/off at the same time.

So can any one point out the problem with this design please? I know this might sound retarded, but please help.

Thanks a lot!