Ravinder487

Full Member level 3

- Joined

- Jul 9, 2010

- Messages

- 169

- Helped

- 0

- Reputation

- 0

- Reaction score

- 0

- Trophy points

- 1,296

- Location

- Bangalore, India

- Activity points

- 2,469

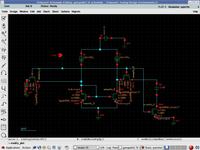

Basic question on capacitors in Spectre

Hi,

I find lot of capacitances in Spectre.Two of them are "cap" in "analogLib" and "nmoscap" in gpdk090.what is the difference between these two.

If I simulate using "cap" it is taking too much of time to charge(around 20ps) and with nmos cap it is <1ps.why is it so.

In the paper I'm referring author has used capacitor formed by three metals(M3 M4 M5).what is the equivalent capacitor in Spectre.

And one last questions what type of capacitors are used in actual ADC and WHY!!?

Thanks&Regards,

Ravinder Jakkidi.

Hi,

I find lot of capacitances in Spectre.Two of them are "cap" in "analogLib" and "nmoscap" in gpdk090.what is the difference between these two.

If I simulate using "cap" it is taking too much of time to charge(around 20ps) and with nmos cap it is <1ps.why is it so.

In the paper I'm referring author has used capacitor formed by three metals(M3 M4 M5).what is the equivalent capacitor in Spectre.

And one last questions what type of capacitors are used in actual ADC and WHY!!?

Thanks&Regards,

Ravinder Jakkidi.

Last edited: